TSMC COUPE: Why the CoWoS Pattern Is Repeating in Silicon Photonics

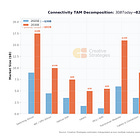

While we understand why, much of the current narrative around the optical market is spent debating when co-packaged optics scales and which active optics vendors benefit first. We think the more important question is who controls the manufacturing platform that the transition depends on. That distinction matters because the connectivity stack is already moving from a secondary infrastructure category toward a first-order AI systems constraint. In our broader work, we have framed connectivity as a market expanding from roughly $25 billion to $35 billion today toward $67 billion to $96 billion by the end of the decade, with high-end transceiver demand accelerating sharply alongside cluster scale. In that context, the foundry that controls the optical manufacturing layer matters more than most investors currently appreciate.

Given multiple discussions with folks at NVIDIA, Broadcom, and Ayar Labs, we felt the foundry discussion around optics was timely, especially around TSMC, in which all three of those companies are customers. TSMC is increasingly positioned to occupy the same role in silicon photonics that it came to occupy in advanced AI packaging. COUPE (Compact Universal Photonics Engine) is a manufacturing platform that combines leading-edge electronic logic, a mature photonics process, and advanced packaging integration in a way competitors cannot yet match at system level. Today, that means a 6nm electronic IC, a 65nm SOI photonic IC, hybrid bonding through SoIC-X, and then a roadmap into CoWoS that lets optical engines move from board-level and substrate-level integration toward eventual interposer-level integration next to the switch ASIC or XPU. TSMC is the only foundry that currently brings all of those pieces together in one stack and under one roof.

TSMC has indicated COUPE can lower power consumption by 40% at the same speed versus conventional micro-bump approaches, or deliver a 170% speed gain at the same power envelope. More broadly, the optical roadmap points to a step down in energy per bit from more than 30 pJ/bit for conventional copper toward under 5 pJ/bit for co-packaged optics on substrate and ultimately below 2 pJ/bit as optical I/O moves onto the interposer. In our Copper to Fiber report, we detail the economics of power savings for optical. It is these kinds of systems-level efficiency gain that changes packaging economics, cluster power budgets, and the competitive position of the foundry, enabling it.

The near-term reality, however, is that this is still an early market. CPO is not yet the cheapest answer. CPO solutions are at least 10% more expensive than comparable optical transceivers, and NVIDIA’s current Quantum-X800 implementation shows why. The switch integrates 72 optical engines and 18 external light sources, and the optical engine alone represents roughly 44% to 45% of the CPO bill of materials. That is a useful reminder that the value is already moving toward semiconductor process content even before CPO becomes the dominant form factor. In other words, the market is paying more upfront for a design that improves power, density, and future scaling.

What makes the foundry discussion interesting is that TSMC is not the only credible player, just the one with the strongest end-state position (with two of the market-leading customers in NVIDIA and Broadcom). GlobalFoundries deserves credit for an earlier start, a real installed base, and a legitimate monolithic integration story through Fotonix. It expects silicon photonics revenue to exceed $1 billion by 2030, and its AMF acquisition is expected to bring more than $75 million of revenue in 2026. Tower is also a key player. The company has meaningful PIC traction, over 50 active silicon photonics customers, a fresh NVIDIA-related 1.6T module engagement, and reported $228 million of silicon photonics revenue in 2025, more than double the prior year. Both companies remain important to the optical value chain. But the comparison shifts once the market moves from standalone optical engines, pluggables, and NPO toward fully integrated CPO. Neither GlobalFoundries nor Tower has TSMC’s combination of fine-node EIC capability and CoWoS-class packaging integration, and that becomes the structural dividing line as optical moves closer to the processor. From our supply chain discussions, whether the customer uses GlobalFoundries or Tower Semi, all roads will still lead back to TSMC, and the attraction of having ALL of your semiconductor manufacturing under one roof is why we believe TSMC will be best positioned over the long-haul.

That is why we think the right way to model this is not through a standalone “CPO revenue line” for TSMC. The direct revenue remains small relative to TSMC’s size for now. The value shows up more indirectly through better advanced packaging utilization, a richer wafer mix across EIC and PIC production, and, most important, strategic leverage. Once customers design optical engines, packaging flows, and qualification cycles around the TSMC stack, the dependency compounds. That is the same pattern investors saw with CoWoS before the financial impact became obvious in reported numbers. Our argument is that silicon photonics is beginning to follow a similar path.

What’s in the full report

A detailed breakdown of how COUPE works, why heterogeneous integration is winning, and why node disparity between EIC and PIC is structural rather than temporary.

A fair comparison of TSMC, GlobalFoundries, and Tower Semi, including where each still matters in pluggables, PICs, NPO, and CPO.

A buy-side framework for underwriting the thesis in the model, including where the economics show up even before direct CPO revenue becomes material.

A 12–18 month monitoring checklist covering qualification milestones, substrate-to-interposer migration, and the proof points that would strengthen or weaken the thesis.

The real bear case: why the bigger risk may be a longer bridge through NPO and detachable optical architectures, rather than outright displacement of TSMC.

Ecosystem evidence from NVIDIA, Broadcom, and Ayar Labs showing where product gravity is already forming in the optical stack.